# **RIGOL**

## **Declassification Guide**

# MSO5000 / MSODS7000/MSO8000 Digital Oscilloscope

Aug. 2019

RIGOL (SUZHOU) TECHNOLOGIES INC.

### MSO5000/ MSODS7000/MSO8000 Series

MSO5000 series oscilloscope consists of MSO5354, MSO5204, MSO5104, MSO5102, MSO5074 and MSO5072.

MSODS7000 series oscilloscope consists of MSO7054, MSO7034, MSO7024, MSO7014, DS7054, DS7034, DS7024 and DS7104.

MSO8000 series oscilloscope consists of MSO8204, MSO8104 and MSO8064.

#### **Instrument Memory**

This section contains information on the types of memory available in your instrument. It explains the size of memory, how it is used, its location, volatility and the clearing procedure.

#### Instrument memory:

| Memory type and size                      | Writable during  | Data<br>retained | Purpose/<br>contents              | Data input method             | Location in instrument    | Sanitization procedure |

|-------------------------------------------|------------------|------------------|-----------------------------------|-------------------------------|---------------------------|------------------------|

|                                           | normal operation | when powered off |                                   |                               | and remarks               |                        |

| FRAM<br>64kb                              | Yes              | Yes              | System setting\<br>License Data   | System                        | Main board in CPU area    | Default all settings   |

| Data Memory<br>GPU<br>(SRAM)<br>36Mb×2    | Yes              | No               | System data\ GUI Display          | System                        | Main board in<br>CPU area | Cycle power            |

| Main Code\ FPGA Firmware (Nand Flash) 8Gb | Yes              | Yes              | System firmware\ Calibration data | Firmware upgrade\ Calibration | Main board in<br>CPU area | No user data is stored |

| Boot<br>(SPI Flash)<br>128Mb              | No               | Yes              | Boot loader                       | воот                          | Main board in CPU area    | No user data is stored |

| Data Memory<br>(DDR3)<br>2Gb×2            | Yes              | No               | FPGA Code\ caches                 | System                        | Main board in<br>CPU area | Cycle power            |

| Data Memory<br>(DDR3)<br>2Gb×5            | Yes              | No               | FPGA Code\ caches                 | System                        | Main board in SPU area    | Cycle power            |

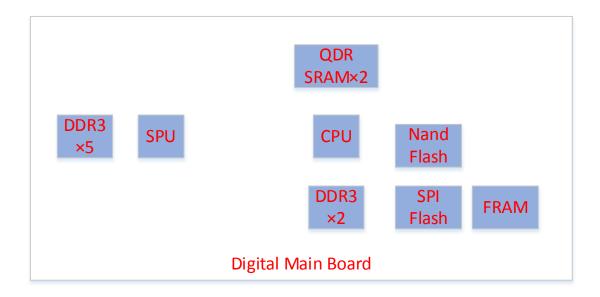

## **Position of Instrument Memory on Main Board**